Entegre Devrelerin Die ve Kılıf Boyutları Arasındaki Farklar

Platformumuzdaki en çok okunan ve popüler makaleleri görmek için Trendler bölümüne geçebilirsiniz.

Entegre devrelerde (IC) die olarak adlandırılan silikon çekirdeğin boyutu ile dış kılıf (paket) boyutu arasında bazen oldukça büyük farklar gözlemlenebilir. Bu fark, tasarım ve üretim süreçlerinin teknik gereksinimlerinden kaynaklanır ve genellikle "anlamsız" ya da "gereksiz" olarak yorumlanabilir. Ancak bu durumun ardında mantıklı sebepler vardır.

Die ve Kılıf Boyutunun Belirleyicileri

Ayrıca Bakınız

Pin Sayısı ve Standart Pin Aralıkları

Bir IC'nin dış kılıfının boyutu, üzerinde bulunan pinlerin sayısı ve bu pinlerin aralarındaki standart mesafelerle doğrudan ilişkilidir. Özellikle Dual Inline Package (DIP) gibi eski paketleme teknolojilerinde, pinler belirli standart aralıklarda yerleştirilir. Bu nedenle, çok sayıda pine sahip bir IC'nin dış kılıfı, die boyutundan çok daha büyük olmak zorundadır. Pinlerin sayısı, IC'nin dış dünya ile iletişim kurmasını sağlar ve bu iletişim için yeterli alan gereklidir.

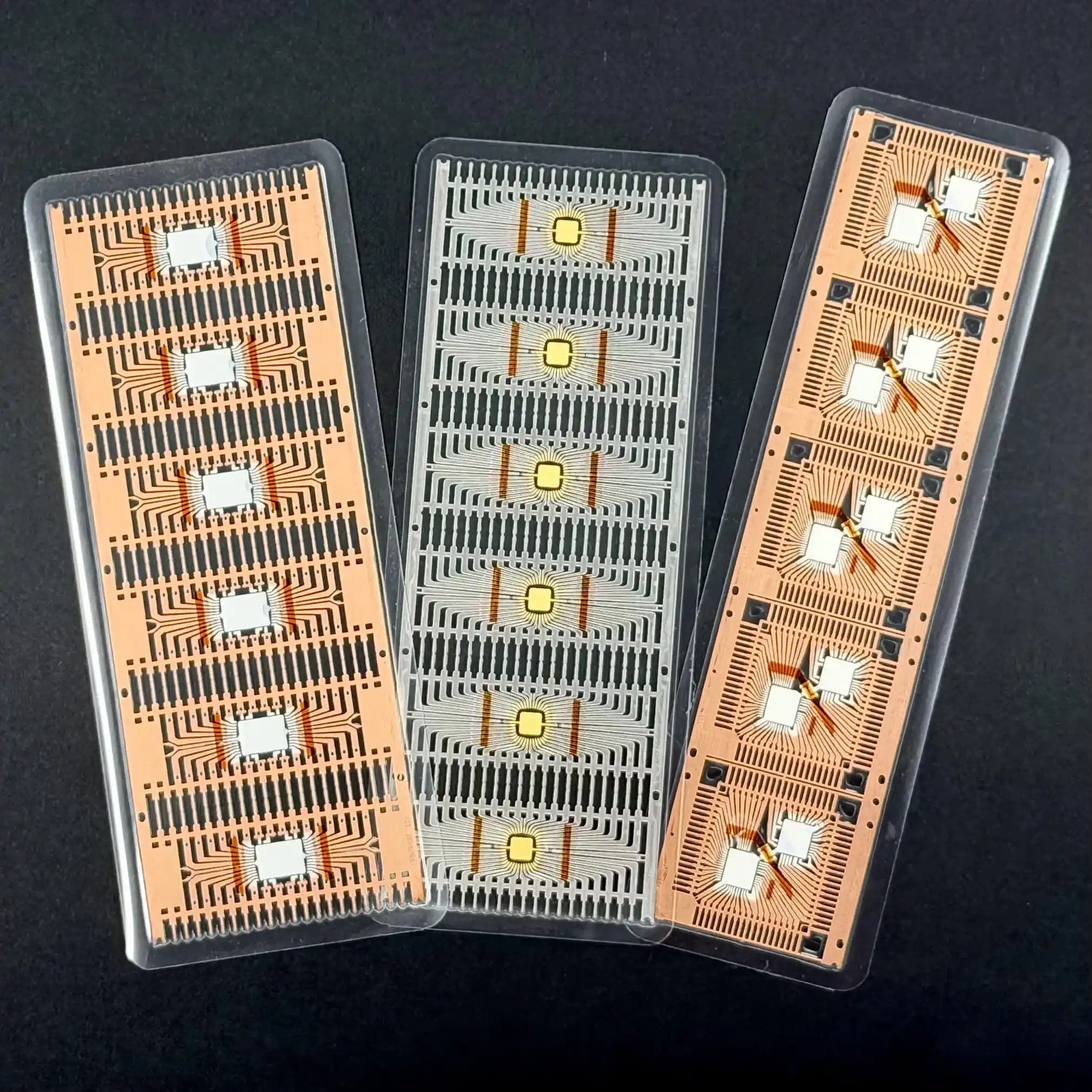

Paketleme Teknolojilerinin Evrimi

Ball Grid Array (BGA) gibi daha gelişmiş paketleme teknolojileri, pinlerin (bilyelerin) çok daha sık ve farklı düzenlerde yerleştirilmesine olanak tanır. Bu sayede PCB tasarımı daha karmaşık hale gelir ancak die boyutu ile kılıf boyutu arasındaki fark azalır. Ancak, BGA ve benzeri teknolojiler, özellikle 1990'ların başında yaygın değildi ve küçük yüzey montaj (SMD) ayak izleri henüz standartlaşmamıştı.

Gelişmiş Mikroişlemciler ve Die Boyutu

Örneğin, Intel'in ilk nesil Atom işlemcileri, bir kuruşun üzerine 11 adet sığacak kadar küçük die boyutlarına sahipti. Buna rağmen, bu işlemcilerin destek çipleri (chipset ve southbridge) daha büyük die boyutlarına ve paketlere sahipti. Bu durum, işlemcinin fonksiyonları ve üretim teknolojisi ile doğrudan ilişkilidir.

Die ve Kılıf Arasındaki Farkın Teknik Sebepleri

I/O Pad Kısıtlamaları

Birçok mikroişlemci ve entegre devre, giriş/çıkış (I/O) pad sayısı ile sınırlıdır. Bu padler, die üzerinde sinyallerin dışarıya çıkması için gereklidir. Dolayısıyla, die boyutu küçüldükçe, bu padlerin yerleşimi ve sayısı dış kılıfın büyüklüğünü etkiler.

Paketleme Kısıtlamaları ve Kapasite

Bazı tasarımlar, paketleme kısıtlamaları nedeniyle die içine sığdırılabilecek kapı (gate) sayısını sınırlar. Bu durum, die boyutunun küçültülmesi için yapılan tasarım tercihlerinin dış kılıf boyutunu etkilemesini sağlar.

Isı ve Mekanik Dayanıklılık

DIP paketler gibi eski teknolojilerde, die'nin mekanik olarak korunması ve ısı dağılımının sağlanması için daha büyük kılıflar kullanılır. Ayrıca, die'nin ısıya maruz kalması durumunda (örneğin 1000°C civarı) die'nin zarar görmemesi için kılıfın dayanıklı olması gerekir.

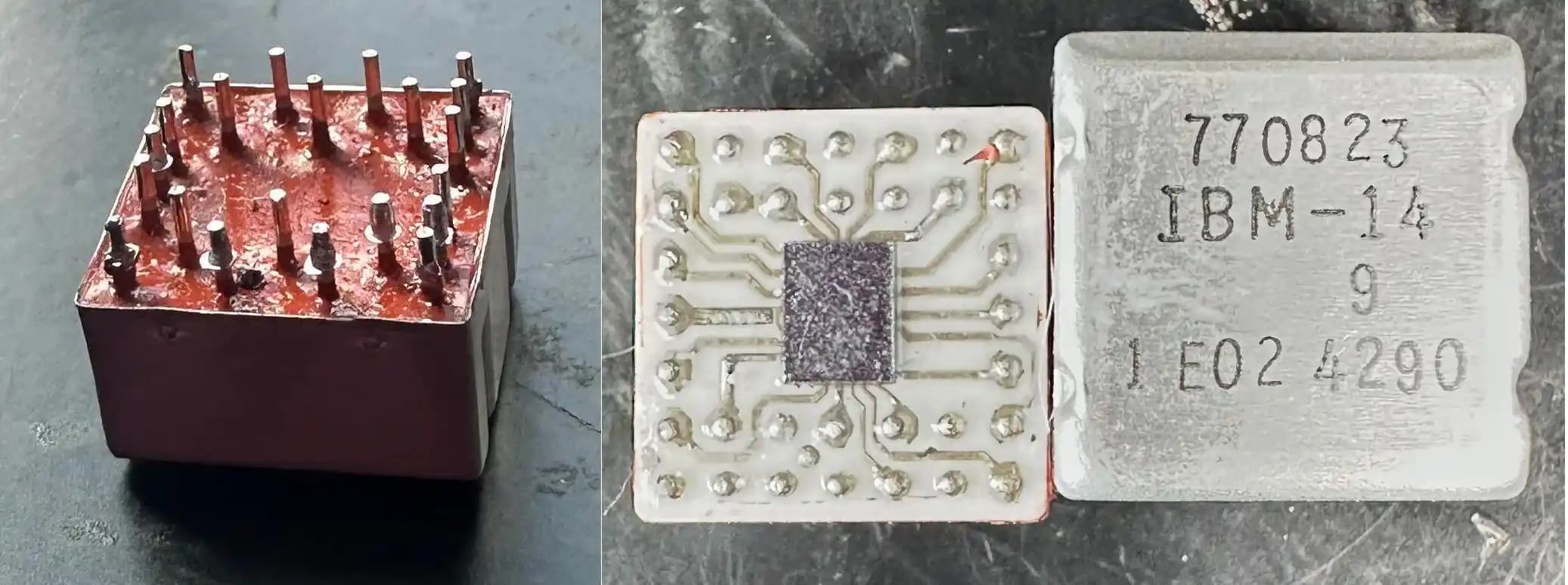

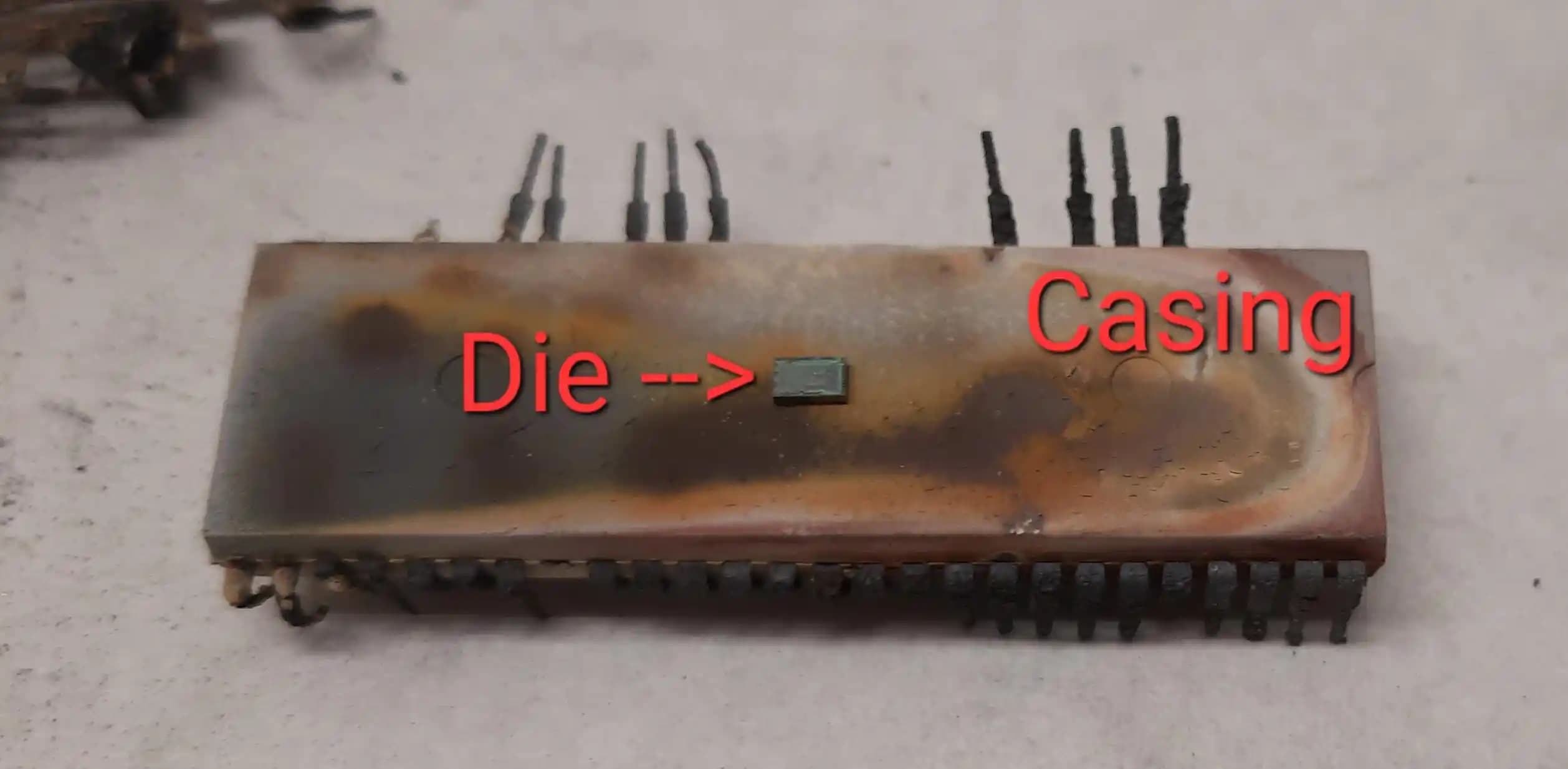

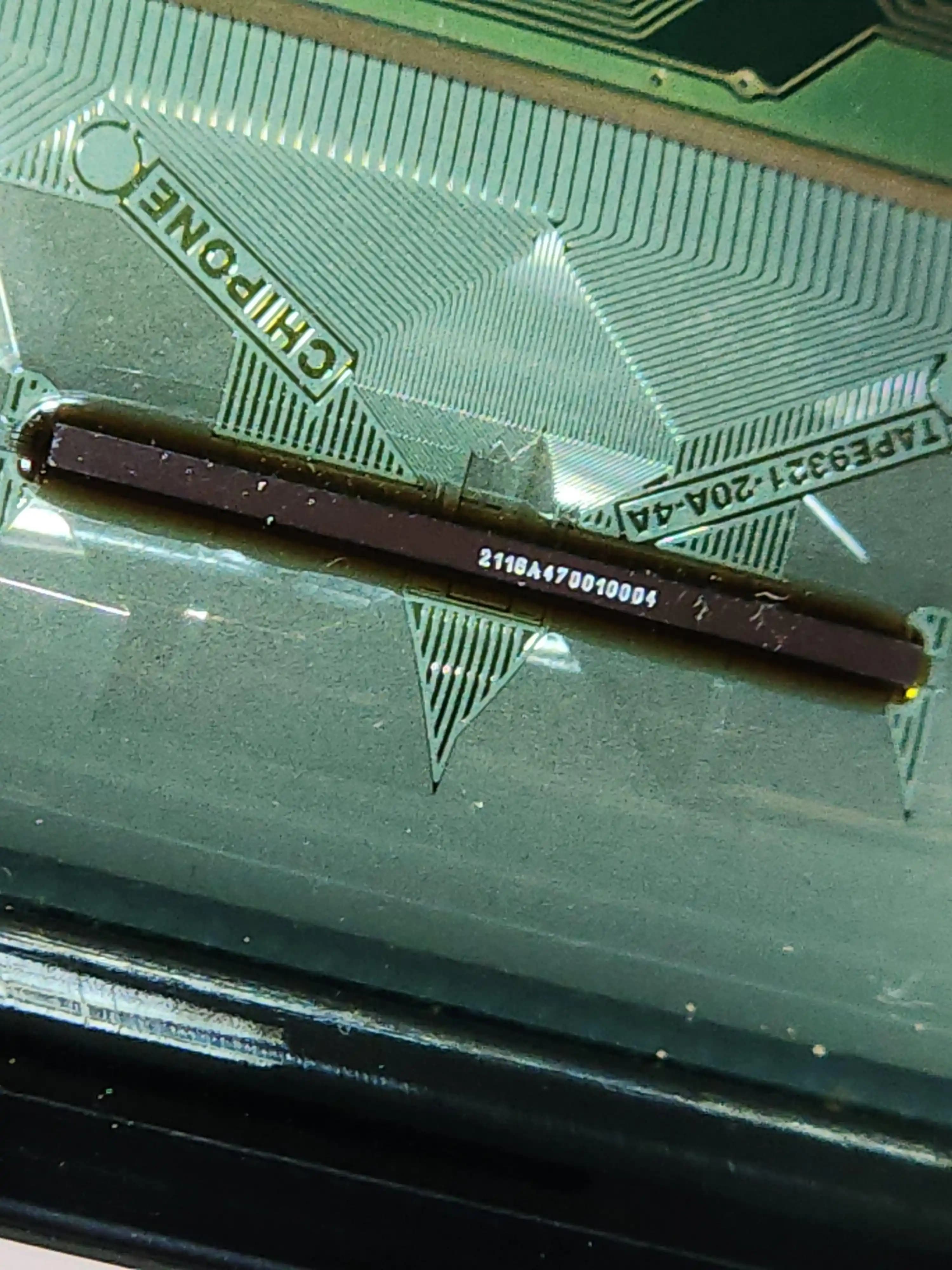

Die Görüntüleri ve İncelemeler

Mikroskop altında die görüntüleri, die ile kılıf arasındaki boyut farkını net şekilde gösterir. Örneğin, NE555 entegresinin farklı üreticilere ait die'leri farklı boyutlarda olabilir. Ayrıca, bazı eski DIP paketler, die'nin küçüklüğünü ve kılıfın büyüklüğünü gözler önüne serer.

Modern Paketleme ve Gelecek Perspektifi

Günümüzde System-on-a-Chip (SoC) teknolojileri, PCB lehimleme karmaşasını azaltmak için tüm bileşenleri silikon üzerinde entegre etmeye çalışır. Ancak, die içinde kablosuz veri transferi gibi yenilikler olmadıkça, dış kılıf ve pinler aracılığıyla iletişim devam edecektir.

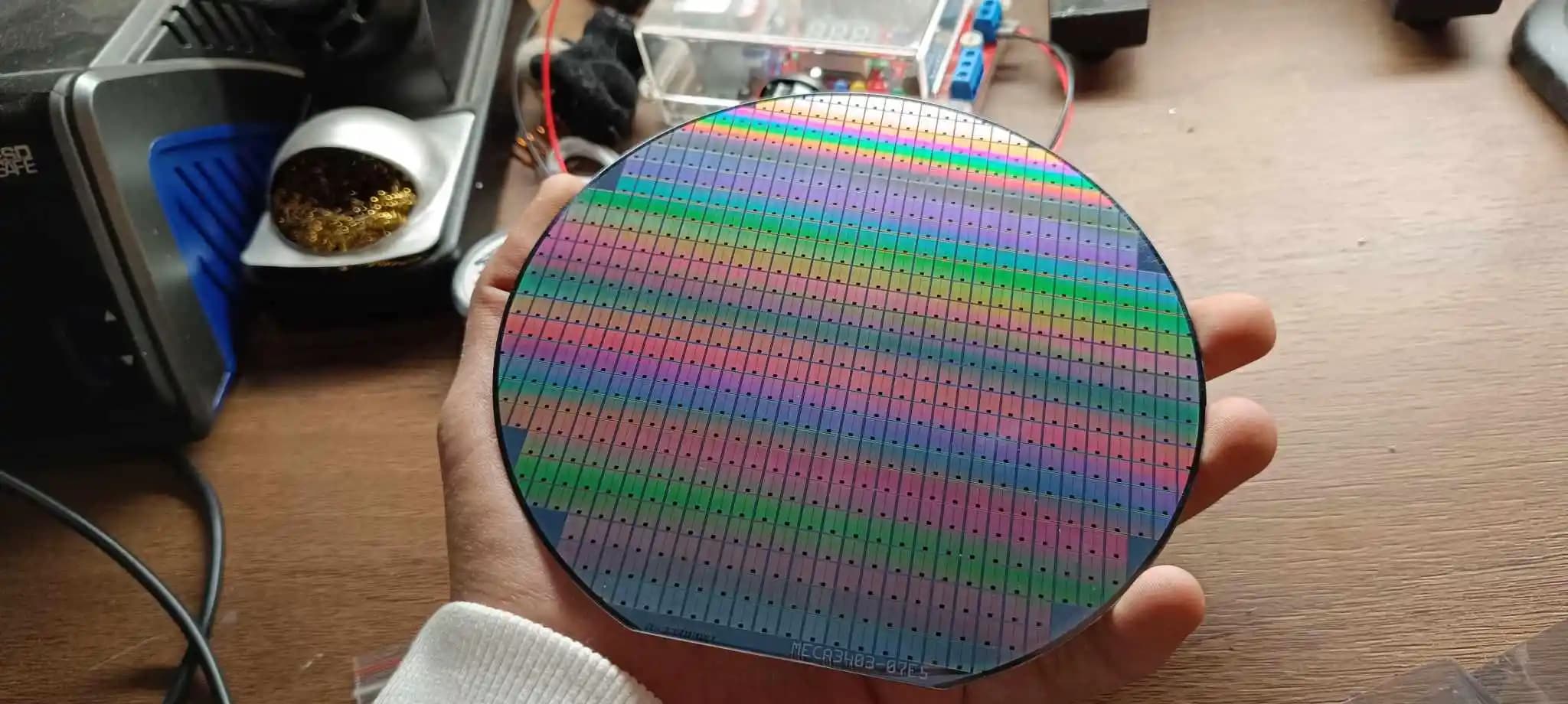

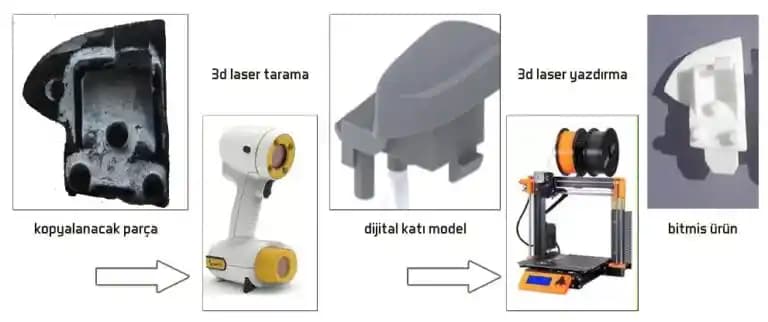

Ayrıca, bazı modern paketleme yöntemleri (Wafer Level Packaging - WLP, Wafer Level Chip Scale Package - WLCSP) die'nin doğrudan paket olarak kullanılmasıyla boyut farkını minimize eder.

"Entegre devrelerin die'si küçüktür ama dış kılıf, pin sayısı ve standartları nedeniyle büyük olabilir. Bu, tasarımın ve üretimin doğal bir sonucudur."

Bu fark, elektronik tasarım ve üretim süreçlerinde karşılaşılan önemli bir konudur. Die ve kılıf arasındaki boyut farkı, teknolojik gelişmelerle birlikte değişmekte ancak tamamen ortadan kalkmamaktadır.

Kaynaklar

https://reddit.com/r/electronics/comments/1k2x6nc/the_size_difference_between_an_integrated/